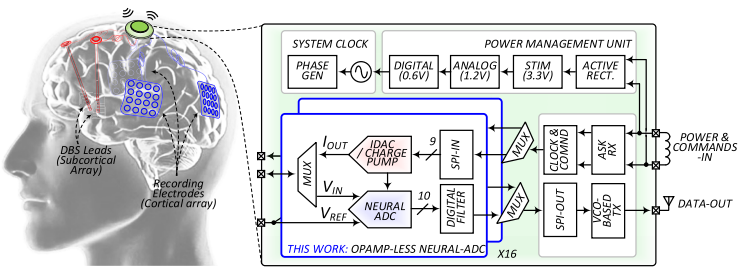

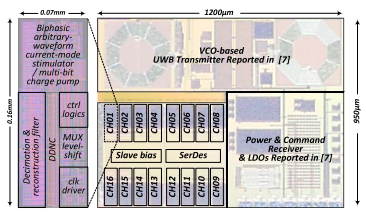

The presented 16-channel Δ-modulated neural analog-to-digital converter (ADC) exhibits tolerance to input dc offsets of any value, up to the supply voltage. It employs a dynamic differential-difference comparator architecture with a super-GΩ input impedance ensuring negligible gate-leakage current and well-matched differential inputs resulting in more than 78 dB of rejection of common-mode signals and artifacts. The all-digital nature of the presented Δ -ADC enables sampling of input signals at high oversampling ratios (OSRs) making the front-end immune to stimulation artifacts with differential amplitudes up to a limit that is scalable by the OSR (e.g., 10 mVPP at OSR = 10 k). Moreover, it allows the Δ-ADC to linearly scale down the power consumption required by the application’s recording bandwidth. The oversampled Δ-ADC achieves an effective number of bits (ENOB) of 9.7-bit and 2.6-μVRMS integrated input-referred noise over 1 Hz to 500-Hz bandwidth. It uses no large passives or statically biased circuits, such as operational amplifiers (Opamps) saving both channel area (0.011 mm²) and power consumption (0.99 μW). Experimentally measured results validate the key features of the design and include in vivo recordings in freely moving guinea pigs. The fabricated prototype system-on-a-chip (SoC) hosts an array of 16-channel neural-ADC with in-channel digitally programmable high-compliance current-mode biphasic stimulators as well as wireless circuitry for data communication and power/command reception.